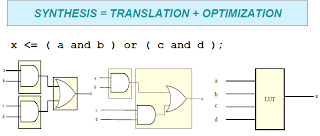

• Synthesis is an automatic process that converts user’s hardware description into structural logic description.

• When we use VHDL as textual file, the process is called VHDL Synthesis.

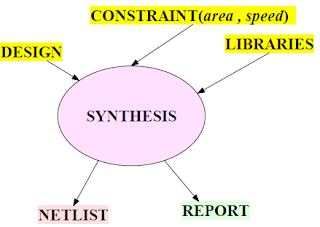

• Synthesis is a means of converting HDL into real world hardware.

• Synthesis tools generate a gate-level netlist for the target technology.

• Synthesis is target device technology specific.

• Synthesizer will try to use the best architectural resource available with the target.

Several steps work out behind the scene!

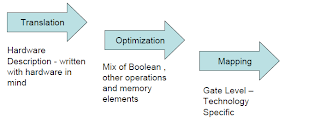

• Translation ( language synthesis ) : Design at higher level of description is compiled into known language elements.

• Optimization : Algorithms are applied to make the design compact and fast.

• Design is mapped using architecture specific techniques.

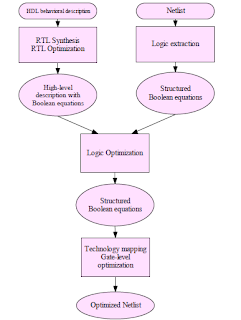

Synthesis process – design flow

Synthesis process

• Translation : Inputs are transformed into a description based Boolean equations.

– If the input data consists of gate level netlist then it is necessary to extract Boolean equations to determine functionality of all used gates.

• Technology independent logic optimization: This process aims to improve structure of Boolean equations by applying rules of Boolean algebra . This removes the redundant logic and reduces the space requirement.

• Technology Mapping: This is the process of transforming technology independent netlist into technology dependent one. During mapping , timing and area information of all usable gates of the target technology must be available. It is split into two phases.

– Flattening

– Structuring

Flattening

• The aim is to generate Boolean equations for each output of module in such a way that the output value is a direct function of inputs. These equations reflect two level logic in SOP form.

• Resulting equations do not imply any structure.

• Good optimization results are obtained.

• Caution: In case of structured logic this process would destroy the characteristic structure and its associated properties . e.g. carry look ahead adder.

• Flattening cannot be applied to every logic circuit because the number of product terms may become very large.

Structuring

• New intermediate variables are inserted during the structuring process.

• E.g. If (A’.B’.C’) occurs 10 times then the tool may assign X= (A’.B’.C’) and use X everywhere.

• Finally , the sub-functions are substituted into original equations.

• Compared to the logic before structuring, the resulting area is reduced.

Synthesis process- review

• Translation process converts RTL to a Boolean form.

• Optimization is done on the converted Boolean equations.

• Optimized logic is mapped to technology library.

• Flattening is a process where all the design hierarchy is removed, the entire design is transformed into a flat , generic , SOP form.

• Structuring is the opposite of flattening, its adds structure to the generic design by extracting common logic factors and representing them as intermediate nodes to produce compact logic.

information shared by www.irvs.info

No comments:

Post a Comment