– Structural

– Data flow

– Behavioral

Structural Method

• At the structural level, which is the lowest level, you have to first manually design the circuit.

• Use VHDL to specify the components and gates that are needed by the circuit and how they are connected together by following your circuit exactly.

• Synthesizing a structural VHDL description of a circuit will produce a netlist that is exactly like your original circuit.

• The advantage of working at the structural level is that you have full control as to what components are used and how they are connected.

• But you need to first come up with the circuit and so the full capabilities of the synthesizer are not utilized.

Dataflow Method

• At the dataflow level, you use the built-in logical functions of VHDL in signal assignment statements to describe a circuit, which again you have to first design manually.

• Boolean functions that describe a circuit can be easily converted to signal assignment statements using the built-in logical functions.

• The only drawback is that the built-in logical functions such as the AND and OR function only take two operands. This is like having only 2-input gates to work with!

NOTE: All the statements use in the structural and dataflow level are executed concurrently

Behavioral Method

• Describing a circuit at the behavioral level is most similar to writing a computer program.

• You have all the standard high-level programming constructs such as the FOR LOOP, WHILE LOOP, IF THEN ELSE, CASE, and variable assignments.

• The statements are enclosed in a process block and are executed sequentially.

Example

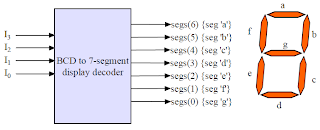

BCD to 7- segment display decoder

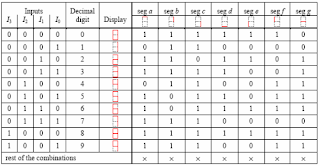

Truth-table

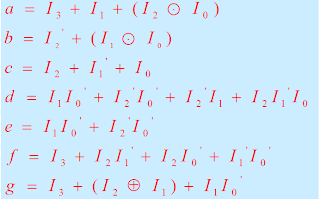

Logic Equations

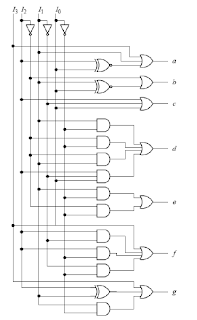

Logic gates

information shared by www.irvs.info