A good synthesis tool should

– perform technology specific optimizations i.e. vendor specific FPGAs and CPLds.

– have best optimization techniques.

– allow designer control.

– have broad language coverage.

– provide user friendly debugging environment.

– have fast compile times.

– provide clean and seamless link with back end tools.

Features

Tool cost depends on features provided by it

Desirable features are:

– Replicating the logic.

– Duplicate flip-flops, remove unused logic.

– optimization across design hierarchy.

– resource sharing of adders , incrementors, multipliers.

– automatic RAM inference (RAM logic is automatically mapped to technology specific RAM cells).

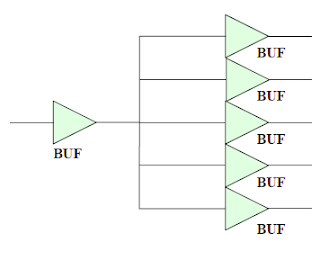

Replicate logic

– Replicate logic to meet fan-out demands.

– E.g. WR’ may be connected to 100 points hence add buffers to split internally.

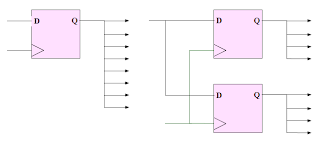

Duplicating logic

• We can duplicate the logic which generates the signal , for minimizing fan-out.

• Trade-off : Loading effect of signals is reduced hence lowering propagation delay but at the cost of logic and interconnect complexity.

information shared by www.irvs.info