• when … else

• with … select

NOTE: These constructs need not be in the process.

when…else

• A concurrent statement which assigns one of several expressions to a signal, depending on the values of Boolean conditions which are tested in sequence.

• Equivalent to a process containing an if statement.

Syntax

[Label:] Target <= [Options]

Expression [after TimeExpression] when Condition else

Expression [after TimeExpression] when Condition else

...

Expression [after TimeExpression] [when Condition];

Where to use ?

architecture – begin – HERE - end

block – begin – HERE - end

generate – begin – HERE - end

Rules:

• The reserved word guarded may only appear in a signal assignment within a guarded block. A guarded assignment only executes when the guard expression on the surrounding block is true.

• An Expression on the right hand side may be replaced by the reserved word “unaffected”.

Synthesis

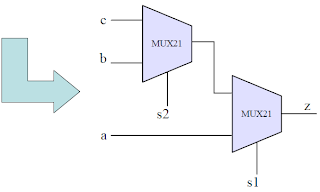

• Conditional signal assignments are synthesized to combinational logic.

• The Expressions on the right hand side are multiplexed onto the Target signal.

• The resulting logic will be priority encoded, because the conditions are tested in sequence.

Remarks:

• Conditional and selected signal assignments are a concise way to describe combinational logic in Register Transfer Level descriptions, although processes can be easier to read and maintain in some cases.

• A conditional assignment is a neat way to convert from a Boolean condition to the type Std_logic.

Example

z <= a when s1=‘1’

else

b when s2=‘1’

else

c ;

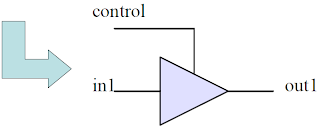

Example (Tri-state Buffer)

architecture tri_buff of tri_buff_part is

begin

out1 <= in1 when control=‘1’

else

‘z’;

end tri_buff ;

information shared by www.irvs.info