• PROCESS cannot have a sensitivity list when WAIT is employed.

• Three flavours of WAIT statements are:

– WAIT UNTIL

– WAIT ON

– WAIT FOR

Syntax

WAIT UNTIL signal_condition;

• The WAIT UNTIL statement accepts only one signal, thus being more appropriate for synchronous code than asynchronous.

• Since the PROCESS has no sensitivity list in this case, WAIT UNTIL must be the first statement in the PROCESS.

• The PROCESS will be executed every time the condition is met.

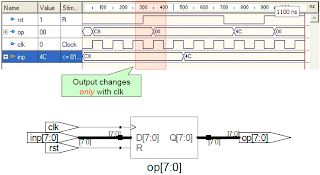

Example ( 8-bit register )

PROCESS -- no sensitivity list

BEGIN

WAIT UNTIL (clk'EVENT AND clk='1');

IF (rst='1') THEN

op <= "00000000";

ELSIF (clk'EVENT AND clk='1') THEN

op <= inp;

END IF;

END PROCESS;

Output and Inference

Syntax

WAIT ON signal1 [, signal2, ... ];

• The WAIT ON statement accepts multiple signals.

• The PROCESS is put on hold until any of the signals listed changes.

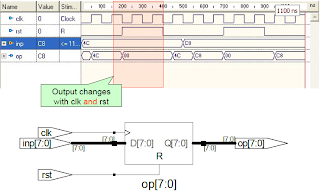

Example ( 8-bit register )

PROCESS

BEGIN

WAIT ON clk, rst;

IF (rst='1') THEN

op <= "00000000";

ELSIF (clk'EVENT AND clk='1') THEN

op <= inp;

END IF;

END PROCESS;

Output and Inference

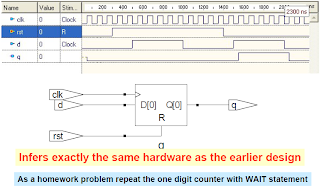

DFF revisited with WAIT!

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY dff IS

PORT (d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC);

END dff;

ARCHITECTURE dff OF dff IS

BEGIN

PROCESS

BEGIN

WAIT ON rst, clk;

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END dff;

Output and Inference

Syntax

WAIT FOR time;

• WAIT FOR is intended for simulation only

(waveform generation for test-benches)

information shared by www.irvs.info